本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.ldbm.cn/p/439707.html

如若内容造成侵权/违法违规/事实不符,请联系编程新知网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

Windows11电脑上自带的画图软件修改照片大小(不裁剪尺寸的情况下)

针对一张图片,有时候上传的图片有大小限制,那么在这种情况下如何修改其大小呢,在不裁剪尺寸的情况下 步骤如下:

1.选定一张图片,右击->打开方式->画图,如下: 第二步:打开图片…

FreeRTOS学习笔记—②RTOS的认识及任务管理篇

由于正在学习韦东山老师的RTOS课程,结合了网上的一些资料,整理记录了下自己的感悟,用于以后自己的回顾。如有不对的地方请各位大佬纠正。 文章目录 一、RTOS的优势二、RTOS的核心功能2.1 任务管理2.1.1 任务的创建2.1.2 任务的删除*2.1.3 任…

(计算机网络)运输层

一.运输层的作用 运输层:负责将数据统一的交给网络层 实质:进程在通信 TCP(有反馈)UDP(无反馈) 二.复用和分用 三. TCP和UDP的特点和区别 进程号--不是固定的 端口号固定--mysql--3306 端口--通信的终点 …

AF高可用性-主备非镜像(路由模式)

实验拓扑 主机基本配置

接口和心跳接口

eth1 eth2 eth3 心跳口 eth4 路由 地址转换 放通策略 主机高可用配置

在“系统”-“高可用配置”启动双机热备,选择“主备备份“,填入对端心跳接口IP。数据同步接口可选。这里配置主备非镜像,镜像模…

安卓玩机工具------小米工具箱扩展工具 小米机型功能拓展

小米工具箱扩展版 小米工具箱扩展版 iO_Box_Mi_Ext是由晨钟酱开发的一款适用于小米(MIUI)、多亲(2、2Pro)、多看(多看电纸书)的多功能工具箱。该工具所有功能均可以免root实现,使用前&…

博客摘录「 深度学习 | 编码器-解码器网络、seq2seq模型、束搜索算法」2024年9月7日

老师在课上是这样引入的: Sequence to Sequence Learning:两个循环神经网络组成。

红色部分和绿色部分都是RNN。

预测任务就是从一个序列到另一个序列。

第一个序列称之为原序列,第二个序列称为目标序列。两者…

[数据集][目标检测]血细胞检测数据集VOC+YOLO格式2757张4类别

数据集格式:Pascal VOC格式YOLO格式(不包含分割路径的txt文件,仅仅包含jpg图片以及对应的VOC格式xml文件和yolo格式txt文件) 图片数量(jpg文件个数):2757 标注数量(xml文件个数):2757 标注数量(txt文件个数):2757 标注…

【H2O2|全栈】Markdown | Md 笔记到底如何使用?【前端 · HTML前置知识】

Markdown的一些杂谈

目录

Markdown的一些杂谈 前言

准备工作

认识.Md文件

为什么使用Md?

怎么使用Md?

编辑

怎么看别人给我的Md文件?

Md文件命令

切换模式

粗体、倾斜、下划线、删除线和荧光标记

分级标题

水平线

引用

无序…

多个vue项目部署到nginx服务器

文章目录 需求一、项目打包1.vue.config.js2.request.js文件3.打包 二、nginx配置 需求

同一个域名安装多个vue项目。

比如:域名为 https://domain.com 后缀。那么通过不同的后缀就能去访问不同的项目地址。

https://domain.com,不加任何后缀&#x…

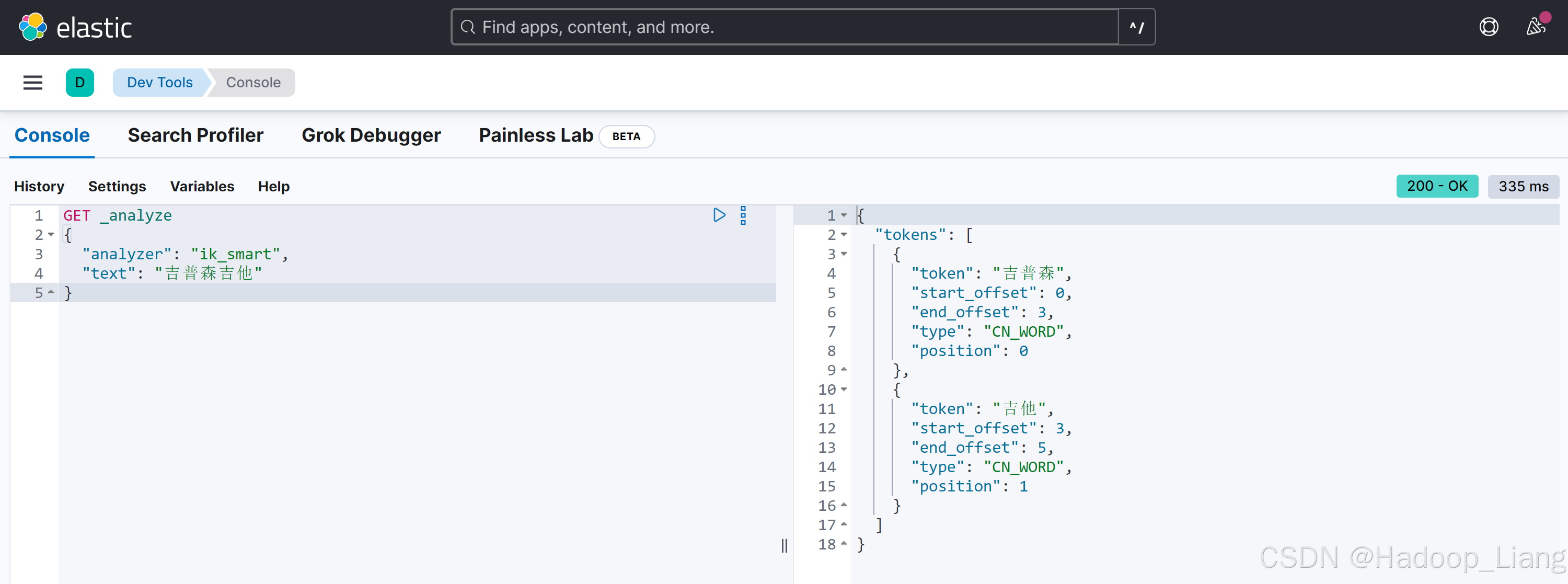

Windows下安装ELK8(elasticsearch、logstash、kibana)及相关工具插件

目录

概述

ELK简介

安装elasticsearch

下载elasticsearch

解压

配置不用登录及关闭SSL

启动elasticsearch

访问elasticsearch

安装elasticsearch-head

提前准备node.js

下载elasticsearch-head

解压

浏览器打开index.html

安装kibana

下载kibana

解压

配置kib…

《Rust避坑式入门》第1章:挖数据竞争大坑的滥用可变性

赵可菲是一名Java程序员,一直在维护一个有十多年历史的老旧系统。这个系统即将被淘汰,代码质量也很差,每次上线都会出现很多bug,她不得不加班修复。公司给了她3个月的内部转岗期,如果转不出去就会被裁员。她得知公司可…

【Vue】关于Vue3的生命周期

目录 Vue3中新增了一个setup生命周期函数:(1) setup执行的时机是在beforeCreate生命周期函数之前执行,在setup函数中是不能通过this来获取实例的;(2) 为了命名的统一性,将beforeDestroy 改名为 beforeUnmount,destroye…

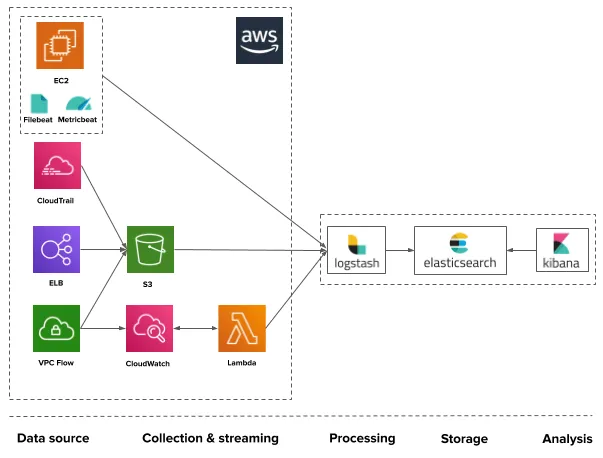

使用 ELK Stack 进行云原生日志记录和监控:AWS 中的开发运营方法

使用 ELK Stack 进行云原生日志记录和监控 欢迎来到雲闪世界。在当今的云原生世界中,日志记录和监控是强大的 DevOps 策略的重要组成部分。监控应用程序性能、跟踪错误和分析日志对于确保无缝操作和主动识别潜在问题至关重要。在本文中,我们将指导您使用…

每日一题,力扣leetcode Hot100之238.除自身以外数组的乘积

乍一看这个题很简单,但是不能用除法,并且在O(N)时间复杂度完成或许有点难度。

考虑到不能用除法,如果我们要计算输出结果位置i的值,我们就要获取这个位置左边的乘积和右边的乘积,那么我新设立两个数组L和R。

对于L来…

Open Source, Open Life 第九届中国开源年会论坛征集正式启动

中国开源年会 COSCon 是业界最具影响力的开源盛会之一,由开源社在2015年首次发起,而今年我们将迎来第九届 COSCon! 以其独特定位及日益增加的影响力,COSCon 吸引了越来越多的国内外企业、高校、开源组织/社区的大力支持。与一般企…

【开源大模型生态4】大模型和安卓时刻

开源大模型,指基于开源软件模式,由全球开发者共同参与、共同维护、共同发展的机器学习模型。

我们之前有过关于开源大模型和对应开源协议的探讨:

【AI】马斯克说大模型要开源,我们缺的是源代码?(附一图看…

Chapter 13 普通组件的注册使用

欢迎大家订阅【Vue2Vue3】入门到实践 专栏,开启你的 Vue 学习之旅! 文章目录 前言一、组件创建二、局部注册三、全局注册 前言

在 Vue.js 中,组件是构建应用程序的基本单元。本章详细讲解了注册和使用 Vue 的普通组件的两种方式:…

Vue day-03

目录

Vue常用特性

一.响应更新

1. 1 v-for更新监测

1.2 v-for就地更新

1.3 什么是虚拟DOM

1.4 diff算法更新虚拟DOM

总结:key值的作用和注意点:

二.过滤器

2.1 vue过滤器-定义使用

2.2 vue过滤器-传参和多过滤器

三. 计算属性(computed)

3.1 计算属性-定义使用

3.…

18056 字母统计

### 思路 1. 输入三行字符串。 2. 初始化一个计数器 count 为0。 3. 遍历每个字符串的每个字符,如果是大写字母,则计数器加1。 4. 输出计数器的值。

### 伪代码 1. 初始化 count 为0。 2. 输入三行字符串 line1, line2, line3。 3. 遍历 line1 的每个字…

负载均衡 Ribbon 与 Fegin 远程调用原理

文章目录 一、什么是负载均衡二、Ribbon 负载均衡2.1 Ribbon 使用2.2 Ribbon 实现原理 (★)2.3 Ribbon 负载均衡算法 三、Feign 远程调用3.1 Feign 简述3.2 Feign 的集成3.3 Feign 实现原理 (★) 一、什么是负载均衡

《服务治理:Nacos 注册中心》 末尾提到了负载均…

![[数据集][目标检测]血细胞检测数据集VOC+YOLO格式2757张4类别](https://i-blog.csdnimg.cn/direct/22c867ab717d44c78b985ed667169b42.png)